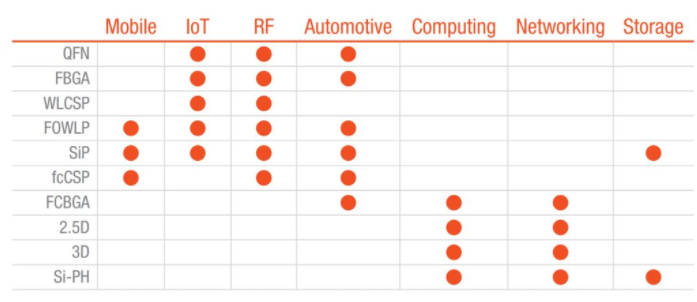

数字 IC 的封装选项(以及相关的流行词和首字母缩略词)继续成倍增加。微处理器、现场可编程门阵列(FPGA) 和专用定制 IC (ASIC) 等高级数字 IC 以多种封装形式提供,例如:QFN——四方扁平无引线; FBGA——细间距球栅阵列; WLCSP——晶圆级封装; FOWLP——扇出晶圆级封装; fcCSP——倒装芯片级封装;和 FCBGA——倒装芯片球栅阵列封装。

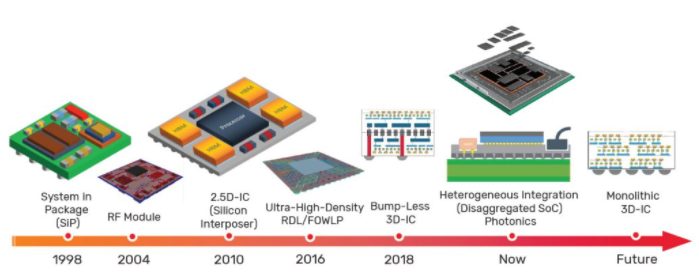

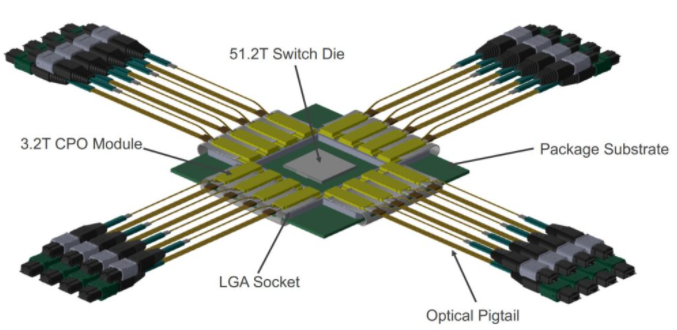

将多个芯片封装在一起的选项包括系统级封装、多芯片模块、芯片级、小芯片、异构、2.5D 和 3D 堆叠等。正在开发的多芯片量子处理器可以解决容错量子计算机的关键扩展挑战。共同封装光学器件 (CPO) 或封装光学器件 (IPO) 正在出现,它们将光学器件和开关硅集成在同一封装中,从而在曾经不相交和独立的技术之间产生协同作用,并节省大量功率。

基于小芯片(Chiplet)的设计、多芯片模块 (MCM) 和系统级封装 (SiP) 是或可以是异构集成的形式,在定义这三种封装风格时存在非常大的灰色区域。一家公司的基于小芯片的设计可能被另一家供应商称为 MCM,而 MCM 和 SiP 通常被归为同一类别。下面回顾了一些细微差别。

小芯片是经过测试的 IP 功能的物理实现,具有在硅晶片上制造的标准通信接口,可通过提高制造产量和跨应用程序的可重用性来降低成本。给定解决方案中的小芯片可以具有不同的工艺节点。小芯片提供标准功能,使设计人员能够专注于设计中的独特 IP。结果被称为“伪 SoC”,其设计速度比完全集成的 SoC 解决方案更快、成本更低。基于小芯片的解决方案通常不包括无源设备或其他“非硅”设备。小芯片解决方案的一个例子可以是当今的一些微处理器,其中处理器内核和 I/O 驻留在通用封装中的不同硅芯片上。

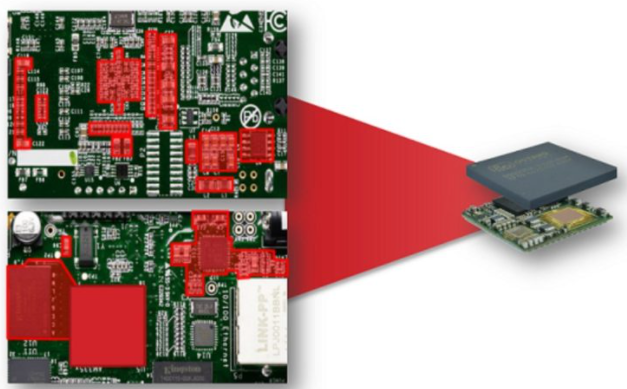

MCM 最初仅集成多个芯片,不包括无源器件或其他组件。 MCM 中的芯片是“完整”的 IC,例如处理器、GPU 和 RF 部分,而不是更简单的单功能小芯片。随着概念的发展,MCM 的尺寸越来越大并集成了额外的组件,于是 SiP 诞生了。 MCM 和 SiP 之间的主要区别在于 MCM 不必是一个完整的系统。根据定义,SiP 是单个封装中的系统。

MCM 是封装中紧密耦合的子系统或模块。 SiP将多个 IC 以及支持的无源器件集成到单个封装中。与 MCM 一样,SiP 可以使用来自最佳单个工艺或工艺节点的硅来优化性能并实现所需的集成。SiP 被设计为一个完整的系统并用作单个组件。

系统级封装 (SiP),有时称为多芯片模块 (MCM),将多个 IC 和无源器件集成到单个封装中。 (图片:Octavo 系统)

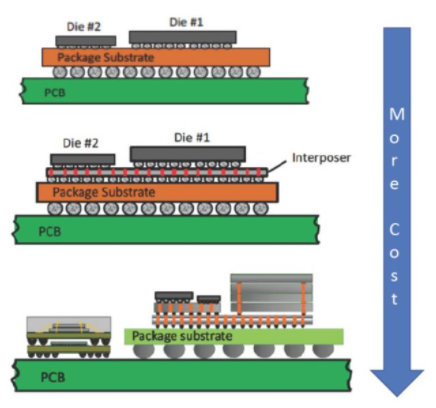

使用硅通孔 (TSV) 互连多个管芯通常被认为是 MCM 或 SiP 与 2.5D 封装器件之间的区别。 TSV 为 MCM 和 SiP 中的有机基板提供了高密度替代品。使用 TSV 可以获得 3D 封装的一些好处,而没有与全 3D 方法相关的挑战和成本。简而言之,与传统的 MCM 或 SiP 解决方案相比,将多个管芯放置在具有非常细间距 TSV 的中介层上会产生互连和更好的重量、尺寸和功率特性。

全3D IC则是更进一步,使用 TSV 在垂直维度上堆叠。它可以产生更小和更高性能的解决方案。 3D 封装是另一种形式的垂直集成,指的是使用引线键合和倒装芯片等互连方法进行 3D 集成。 3D 封装可分为 3D 系统级封装 (3D SiP)、3D 晶圆级封装 (3D WLP) 和 3D 层叠封装 (3D PoP)。与 2.5D 封装相比,各种形式的 3D 封装都有一些缺点,包括:

3D 结构本质上更复杂,修改或升级 2.5D 装配通常更简单、更快。升级 2.5D 器件就像使用新的中介层或用改进版本替换一个或多个芯片一样简单。

2D 封装在封装基板上的单个平面上安装 2 个或更多裸片,2.5D 在裸片和封装基板之间添加一个中介层,3D 堆叠则是在垂直维度进行集成。 (图片:美国宇航局)

使用晶圆级封装 (WLP),晶圆制造工艺扩展到包括晶圆切割之前的器件互连。大多数其他封装首先进行晶圆切割,然后将单个管芯放入塑料封装中并连接焊料凸点。 WLP 在切割晶圆之前将封装的底部和顶部输出层以及焊料凸块连接到 IC。由于封装与裸片的尺寸基本相同,因此 WLP 是芯片级封装 (CSP) 技术的一种形式。

WLP 用于需要尽可能最小的解决方案的应用,例如智能手机。然而,WLP 的局限性在于,由于封装尺寸非常小,可以支持的触点数量有限。在高度复杂和紧凑的系统中,扇出晶圆级封装 (FO-WLP) 增强了标准 WLP 以克服有限的 I/O 功能。

与传统封装相比,FO-WLP 可实现更小的封装尺寸以及改进的散热和电气性能。尽管如此,FO-WLP 还是比 WLP 大,而且 FO-WLP 支持更多数量的触点,但不会增加芯片尺寸。在 FO-WLP 中,首先切割晶圆,然后将芯片精确地重新定位在载体晶圆上,每个芯片周围都有一个扇出区域。模具成型,然后添加焊球。

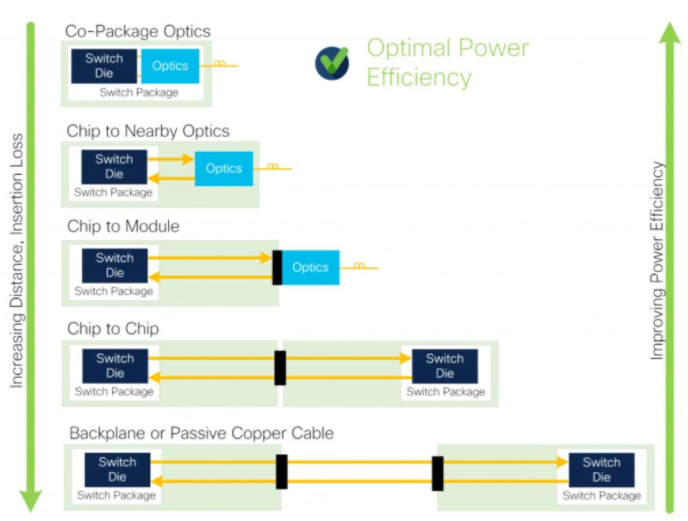

高速数字网络(例如超大规模数据中心)中的序列化-反序列化 (SerDes) 功能通常涉及基于硅的通信链路和基于光的链路之间的接口。随着光学引擎和开关硅之间的距离减小,通道插入损耗也随之下降,从而节省了大量功率。最接近的间距是通过共同封装光学器件 (CPO) 实现的,其中接口的两侧都在一个封装中。

正在开发 CPO 的两项工作是车载光盟 (COBO) 和共同封装光合开发基金会 (CPO JDF)。COBO 已经创建了一个 CPO 工作组,专注于为 CPO 实施制定技术指南和标准。它由对在超大规模数据中心使用 CPO 感兴趣的最终用户和技术供应商组成。COBO 活动主要对 CPO 实施所需的远程激光源和光学连接感兴趣,预计它将与其他 CPO 标准化活动相辅相成。

Facebook 和微软成立了CPO JDF,其主要考虑与 CPO 相关的系统集成问题有关。 CPO JDF 发布了一份产品需求文档 (PRD),描述了旨在提高网络交换机密度和电源效率的 8x400G CPO 模块。 PRD 要求使用 XSR(极短距离)接口。 XSR 针对封装基板上的芯片到光学引擎 (D2OE) 接口和芯片到芯片 (D2D) 接口进行了优化,最大可达约 100 毫米 × 100 毫米。

扩展量子计算机具有挑战性。随着量子处理器尺寸的增加,制造良率下降。实现纠错量子计算需要大量的量子位(qubit)。正在努力将多个较小的芯片连接到一个大规模的量子处理器中。这种多芯片方法有望简化大型量子处理器的创建,并支持该技术的可预测和加速扩展。

缩放是开发容错量子计算机的关键。预计今年晚些时候将测试一个 80 量子位的系统。将多芯片模块技术应用于量子处理器可以产生足够大的系统来运行实际应用,包括所需的纠错。

数字 IC、光互连和量子处理器的封装选择越来越多。先进的封装技术支持异构集成以及使用来自最佳单个工艺或工艺节点的 IC 来优化性能并实现所需的集成。持续的封装开发对于实现从手机到超大规模数据中心的先进系统解决方案非常重要。关键字:封装引用地址:数字IC的高级封装盘点与梳理

TI 基于 FRAM 的 MSP430™ MCU 发挥 WLCSP 封装尺寸优势,帮助优化板级空间,缩小产品尺寸,节省电源。 2014 年 4 月 9 日,北京讯---日前,德州仪器 (TI) 宣布推出几个采用微型封装尺寸的最新超低功耗 MSP430™ 微 (MCU) 系列,帮助开发人员节省宝贵的板级空间。除了 5 个提供微型封装选项的现有 MSP430 MCU 系列之外,TI 基于 FRAM 的超低功耗 MSP430FR5738 以及基于闪存的 MSP430F51x2 MCU 采用小至 2.0 x 2.2 x 0.3 毫米的晶圆芯片级封装 (WLCSP),使开发人员可设计更小的产品。 这些微型封装尺寸使 M

本文提出了一种基于MEMS的 LED芯片 封装技术,利用体硅工艺在硅基上形成的凹槽作为封装led芯片的反射腔。分析了反射腔对 LED 的发光强度和光束性能的影响,分析结果表明该反射腔可以提高芯片的发光效率和光束性能;讨论了反射腔的结构参数与芯片发光效率之间的关系。最后设计r封装的工艺流程。利用该封装结构可以降低芯片的封装尺,提高器件的发光效率和散热特性。 图1 LED T1或T1—3/4 经过几十年的发展,LED性能已经得到了极大的进步,由于它具有发光效率高,体积小,寿命长等优点,将成为新一代 照明 光源,被人们公认为是继白炽灯之后照明领域的又一次重大。目前LED已经在照明、装饰、显示和汽车等诸多领域得到了广泛的应用

光学特性分析 /

稳压器的管脚与封装形式 现简介线性集成稳压器的基本应用(以78XX为例)。图3-1市场了78XX/79XX的管脚与封装形式,集成稳压器作为稳压电源的一般接法。

形式 /

LED的多种形式封装结构及技术 在LED产业链接中,上游是LED衬底晶片及衬底生产,中游的产业化为LED芯片设计及制造生产,下游归LED封装与测试,研发低热阻、优异光学特性、高可靠的封装技术是新型LED走向实用、走向市场的产业化必经之路,从某种意义上讲是链接产业与市场的纽带,只有封装好的才能成为终端产品,才能投入实际应用,才能为顾客提供服务,使产业链环环相扣,无缝畅通。 LED封装的特殊性 LED封装技术大都是在分立器件封装技术基础上发展与演变而来的,但却有很大的特殊性。一般情况下,分立器件的管芯被密封在封装体内,封装的作用主要是保护管芯和完成电气互连。而LED封装则是完成输出电信号,保护管芯正常工作,输出:

新器件缩小封装尺寸60%,增强性能并减少损耗 2022年5月11日—领先于智能电源和智能感知技术的 安森美(onsemi) ,在PCIM Europe展会发布全球首款To-Leadless (TOLL) 封装的碳化硅 (SiC) MOSFET。该晶体管满足了对适合高功率密度设计的高性能开关器件迅速增长的需求。直到最。

杏彩体育官方平台 上一篇:360度解析LED倒装芯片知识 下一篇:苏州高新区:一批重点项目持续“上新”